State of West Virginia Department of Administration Purchasing Division 2019 Washington Street East Post Office Box 50130 Charleston, WV 25305-0130

Solicitation

NUMBER EBA471A PAGE 1

ADDRESS CORRESPONDENCE TO ATTENTION OF:

BVELYN MELTON 04-558-7023

EDUCATIONAL BROADCASTING AUTHORITY 600 CAPITOL STREET

T CHARLESTON, WV 25301-1223

304-558-3400

TYPE NAME/ADDRESS HERE MODOR

RFQ COPY

DATE PRINTED 04/30/2014 **BID OPENING DATE:** 06/12/2014 BID OPENING TIME 1:30PM CAT. LINE QUANTITY UOP ITEM NUMBER UNIT PRICE **AMOUNT** THE WEST VIRGINIA PURCHASING DIVISION IS SOLICITING BIDS ON BEHALF OF THE WEST VIRGINIA EDUCATIONAL BROADCASTING AUTHORITY (EBA) TO ESTABLISH A CONTRACT TO PROVIDE A SITE TO-SITE CONNECTIVITY BETWEEN THREE PROPERTIES OF THE EBA AND TWO WEST VIRGINIA NETWORK (WVNET) LOCATIONS, AS WELL AS INTERNET ACCESS PER THE ATTACHED SPECIFICATIONS AND INSTRUCTIONS TO BIDDERS. d001 УR 205-43 3 SITE-TO-SITE AND INTERNET CONNECTIVITY THIS IS THE END OF REQ EBA471A \*\*\*\*\* TOTAL: SIGNATURE TELEPHONE DATE TITLE FEIN ADDRESS CHANGES TO BE NOTED ABOVE

### INSTRUCTIONS TO VENDORS SUBMITTING BIDS

- 1. REVIEW DOCUMENTS THOROUGHLY: The attached documents contain a solicitation for bids. Please read these instructions and all documents attached in their entirety. These instructions provide critical information about requirements that if overlooked could lead to disqualification of a Vendor's bid. All bids must be submitted in accordance with the provisions contained in these instructions and the Solicitation. Failure to do so may result in disqualification of Vendor's bid.

- 2. MANDATORY TERMS: The Solicitation may contain mandatory provisions identified by the use of the words "must," "will," and "shall." Failure to comply with a mandatory term in the Solicitation will result in bid disqualification.

| 3. | PREB | SID MEETING: The item identified below shall apply to this Solicitation.             |

|----|------|--------------------------------------------------------------------------------------|

|    |      | A pre-bid meeting will not be held prior to bid opening.                             |

|    |      | A <b>NON-MANDATORY PRE-BID</b> meeting will be held at the following place and time: |

A MANDATORY PRE-BID meeting will be held at the following place and time:

Beckley, WV Office - May 16, 2014 @ 10:30 a.m.

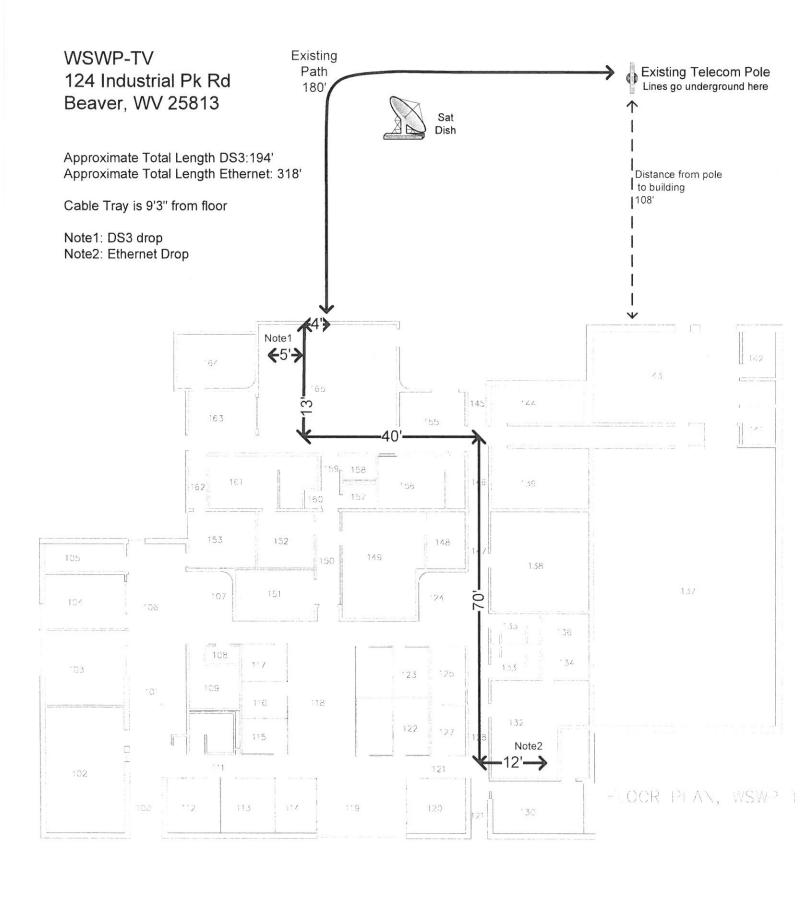

\* 124 Industrial Park Road, Beaver, WV 25813

Morgantown, WV Office - May 19, 2014 @ 11:00 a.m.

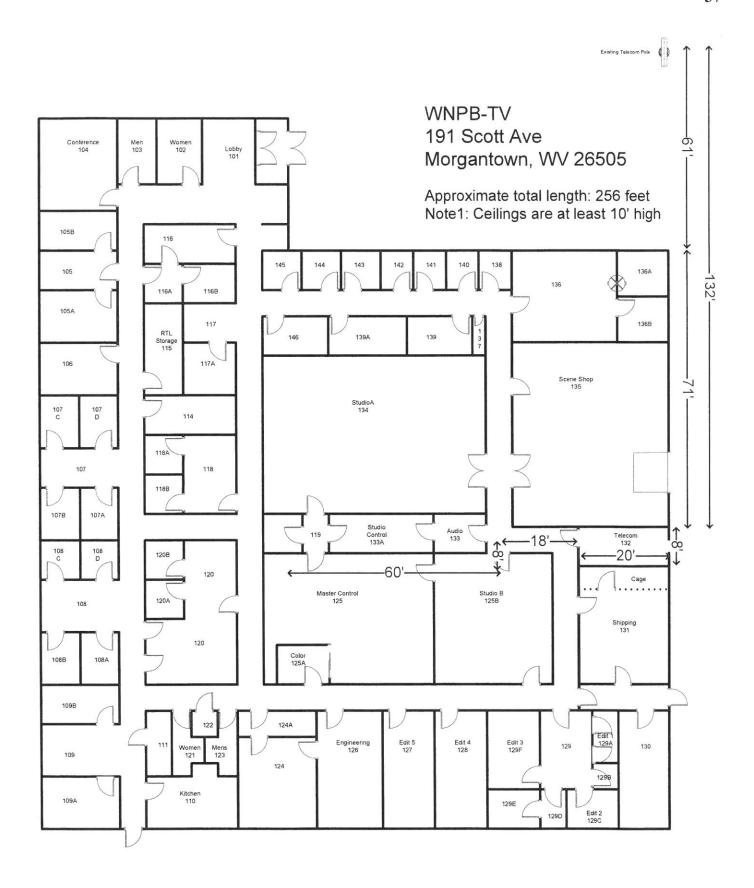

\* 191 Scott Avenue, Morgantown, WV 26505

Charleston, WV Office - MAy 20, 2014 @ 10:30 a.m.

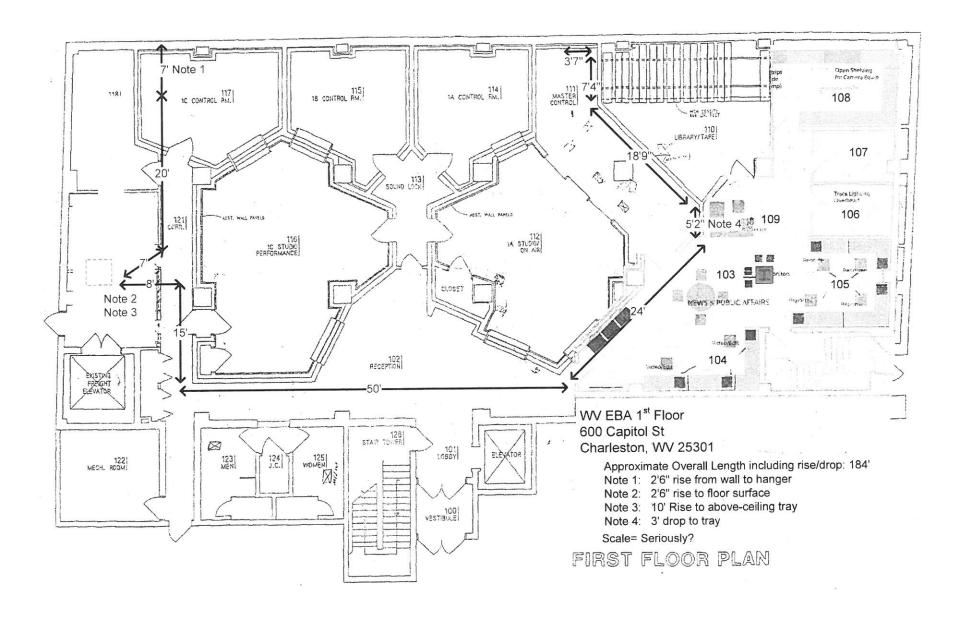

\* 600 Capitol Street, Charleston WV 25301

All Vendors submitting a bid must attend the mandatory pre-bid meeting. Failure to attend the mandatory pre-bid meeting shall result in disqualification of the Vendor's bid. No one person attending the pre-bid meeting may represent more than one Vendor.

An attendance sheet provided at the pre-bid meeting shall serve as the official document verifying attendance. The State will not accept any other form of proof or documentation to verify attendance. Any person attending the pre-bid meeting on behalf of a Vendor must list on the attendance sheet his or her name and the name of the Vendor he or she is representing. Additionally, the person attending the pre-bid meeting should include the Vendor's E-Mail address, phone number, and Fax number on the attendance sheet. It is the Vendor's responsibility to locate the attendance sheet and provide the required information. Failure to complete the attendance sheet as required may result in disqualification of Vendor's bid.

+

All Vendors should arrive prior to the starting time for the pre-bid. Vendors who arrive after the starting time but prior to the end of the pre-bid will be permitted to sign in, but are charged with knowing all matters discussed at the pre-bid.

Questions submitted at least five business days prior to a scheduled pre-bid will be discussed at the pre-bid meeting if possible. Any discussions or answers to questions at the pre-bid meeting are preliminary in nature and are non-binding. Official and binding answers to questions will be published in a written addendum to the Solicitation prior to bid opening.

4. VENDOR QUESTION DEADLINE: Vendors may submit questions relating to this Solicitation to the Purchasing Division. Questions must be submitted in writing. All questions must be submitted on or before the date listed below and to the address listed below in order to be considered. A written response will be published in a Solicitation addendum if a response is possible and appropriate. Non-written discussions, conversations, or questions and answers regarding this Solicitation are preliminary in nature and are non-binding.

Question Submission Deadline: May 23, 2014 -end of business

Submit Questions to: Evelyn P. Melton

2019 Washington Street, East Charleston, WV 25305 Fax: (304) 558-4115

(Vendors should not use this fax number for bid submission)

Email: evelyn.p.melton@wv.gov

- 5. VERBAL COMMUNICATION: Any verbal communication between the Vendor and any State personnel is not binding, including that made at the mandatory pre-bid conference. Only information issued in writing and added to the Solicitation by an official written addendum by the Purchasing Division is binding.

- 6. BID SUBMISSION: All bids must be signed and delivered by the Vendor to the Purchasing Division at the address listed below on or before the date and time of the bid opening. Any bid received by the Purchasing Division staff is considered to be in the possession of the Purchasing Division and will not be returned for any reason. The Purchasing Division will not accept bids, modification of bids, or addendum acknowledgment forms via e-mail. Acceptable delivery methods include hand delivery, delivery by courier, or facsimile. The bid delivery address is:

Department of Administration, Purchasing Division 2019 Washington Street East Charleston, WV 25305-0130

| The bid should contain the information listed considered:                                   | d below on the face of the envelope or the bid may not be                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEALED BID:                                                                                 |                                                                                                                                                                                                                           |

| BUYER:                                                                                      |                                                                                                                                                                                                                           |

| SOLICITATION                                                                                | NO.:                                                                                                                                                                                                                      |

| BID OPENING D                                                                               | ATE:                                                                                                                                                                                                                      |

| BID OPENING T                                                                               | IME:                                                                                                                                                                                                                      |

|                                                                                             |                                                                                                                                                                                                                           |

| technical and one original cost proposal plus<br>Division at the address shown above. Addit | equest for proposal, the Vendor shall submit one original convenience copies of each to the Purchasing ionally, the Vendor should identify the bid type as either a h bid envelope submitted in response to a request for |

| BID TYPE:                                                                                   | Technical Cost                                                                                                                                                                                                            |

| identified below on the date and time listed                                                | esponse to this Solicitation will be opened at the location d below. Delivery of a bid after the bid opening date and time poses of this Solicitation, a bid is considered delivered when ision time clock.               |

| Bid Opening Date and Time: June                                                             | 12, 2014 @ 1:30 P.M.                                                                                                                                                                                                      |

| Bid Opening Location:                                                                       | Department of Administration, Purchasing Division<br>2019 Washington Street East<br>Charleston, WV 25305-0130                                                                                                             |

- 8. ADDENDUM ACKNOWLEDGEMENT: Changes or revisions to this Solicitation will be made by an official written addendum issued by the Purchasing Division. Vendor should acknowledge receipt of all addenda issued with this Solicitation by completing an Addendum Acknowledgment Form, a copy of which is included herewith. Failure to acknowledge addenda may result in bid disqualification. The addendum acknowledgement should be submitted with the bid to expedite document processing.

- **9. BID FORMATTING:** Vendor should type or electronically enter the information onto its bid to prevent errors in the evaluation. Failure to type or electronically enter the information may result in bid disqualification.

7.

### **GENERAL TERMS AND CONDITIONS:**

- 1. CONTRACTUAL AGREEMENT: Issuance of a Purchase Order signed by the Purchasing Division Director, or his designee, and approved as to form by the Attorney General's office constitutes acceptance of this Contract made by and between the State of West Virginia and the Vendor. Vendor's signature on its bid signifies Vendor's agreement to be bound by and accept the terms and conditions contained in this Contract.

- 2. **DEFINITIONS:** As used in this Solicitation/Contract, the following terms shall have the meanings attributed to them below. Additional definitions may be found in the specifications included with this Solicitation/Contract.

- **2.1 "Agency"** or "**Agencies"** means the agency, board, commission, or other entity of the State of West Virginia that is identified on the first page of the Solicitation or any other public entity seeking to procure goods or services under this Contract.

- **2.2 "Contract"** means the binding agreement that is entered into between the State and the Vendor to provide the goods and services requested in the Solicitation.

- **2.3 "Director"** means the Director of the West Virginia Department of Administration, Purchasing Division.

- **2.4 "Purchasing Division"** means the West Virginia Department of Administration, Purchasing Division.

- **2.5 "Purchase Order"** means the document signed by the Agency and the Purchasing Division, and approved as to form by the Attorney General, that identifies the Vendor as the successful bidder and Contract holder.

- **2.6 "Solicitation"** means the official solicitation published by the Purchasing Division and identified by number on the first page thereof.

- **2.7 "State"** means the State of West Virginia and/or any of its agencies, commissions, boards, etc. as context requires.

- **2.8 "Vendor"** or **"Vendors"** means any entity submitting a bid in response to the Solicitation, the entity that has been selected as the lowest responsible bidder, or the entity that has been awarded the Contract as context requires.

days.

|              | <b>TRACT TERM; RENEWAL; EXTENSION:</b> The term of this Contract shall be determined in dance with the category that has been identified as applicable to this Contract below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\checkmark$ | Term Contract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|              | Initial Contract Term: This Contract becomes effective on upon award                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              | and extends for a period of one (1) year(s).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | Renewal Term: This Contract may be renewed upon the mutual written consent of the Agency, and the Vendor, with approval of the Purchasing Division and the Attorney General's office (Attorney General approval is as to form only). Any request for renewal must be submitted to the Purchasing Division Director thirty (30) days prior to the expiration date of the initial contract term or appropriate renewal term. A Contract renewal shall be in accordance with the terms and conditions of the original contract. Renewal of this Contract is limited to two (2) successive one (1) year periods. Automatic renewal of this Contract is prohibited. Notwithstanding the foregoing, Purchasing Division approval is not required on agency delegated or exempt purchases. Attorney General approval may be required for vendor terms and conditions.                                                                                                                                                                                                           |

|              | Reasonable Time Extension: At the sole discretion of the Purchasing Division Director, and with approval from the Attorney General's office (Attorney General approval is as to form only), this Contract may be extended for a reasonable time after the initial Contract term or after any renewal term as may be necessary to obtain a new contract or renew this Contract. Any reasonable time extension shall not exceed twelve (12) months. Vendor may avoid a reasonable time extension by providing the Purchasing Division Director with written notice of Vendor's desire to terminate this Contract 30 days prior to the expiration of the then current term. During any reasonable time extension period, the Vendor may terminate this Contract for any reason upon giving the Purchasing Division Director 30 days written notice. Automatic extension of this Contract is prohibited. Notwithstanding the foregoing, Purchasing Division approval is not required on agency delegated or exempt purchases, but Attorney General approval may be required. |

|              | Release Order Limitations: In the event that this contract permits release orders, a release order may only be issued during the time this Contract is in effect. Any release order issued within one year of the expiration of this Contract shall be effective for one year from the date the release order is issued. No release order may be extended beyond one year after this Contract has expired.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Fixed Period Contract: This Contract becomes effective upon Vendor's receipt of the notice to

proceed and must be completed within

|    |              | One Time Purchase: The term of this Contract shall run from the issuance of the Purchase Order until all of the goods contracted for have been delivered, but in no event shall this Contract extend for more than one fiscal year.                                                                                                                                |

|----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |              | Other: See attached.                                                                                                                                                                                                                                                                                                                                               |

| 4. | receivi      | ICE TO PROCEED: Vendor shall begin performance of this Contract immediately upon ng notice to proceed unless otherwise instructed by the Agency. Unless otherwise specified, the xecuted Purchase Order will be considered notice to proceed                                                                                                                       |

| 5. | _            | NTITIES: The quantities required under this Contract shall be determined in accordance with egory that has been identified as applicable to this Contract below.                                                                                                                                                                                                   |

|    |              | <b>Open End Contract:</b> Quantities listed in this Solicitation are approximations only, based on estimates supplied by the Agency. It is understood and agreed that the Contract shall cover the quantities actually ordered for delivery during the term of the Contract, whether more or less than the quantities shown.                                       |

|    |              | <b>Service:</b> The scope of the service to be provided will be more clearly defined in the specifications included herewith.                                                                                                                                                                                                                                      |

|    | $\checkmark$ | <b>Combined Service and Goods:</b> The scope of the service and deliverable goods to be provided will be more clearly defined in the specifications included herewith.                                                                                                                                                                                             |

|    |              | One Time Purchase: This Contract is for the purchase of a set quantity of goods that are identified in the specifications included herewith. Once those items have been delivered, no additional goods may be procured under this Contract without an appropriate change order approved by the Vendor, Agency, Purchasing Division, and Attorney General's office. |

- 6. PRICING: The pricing set forth herein is firm for the life of the Contract, unless specified elsewhere within this Solicitation/Contract by the State. A Vendor's inclusion of price adjustment provisions in its bid, without an express authorization from the State in the Solicitation to do so, may result in bid disqualification.

- 7. EMERGENCY PURCHASES: The Purchasing Division Director may authorize the Agency to purchase goods or services in the open market that Vendor would otherwise provide under this Contract if those goods or services are for immediate or expedited delivery in an emergency. Emergencies shall include, but are not limited to, delays in transportation or an unanticipated increase in the volume of work. An emergency purchase in the open market, approved by the Purchasing Division Director, shall not constitute of breach of this Contract and shall not entitle the Vendor to any form of compensation or damages. This provision does not excuse the State from fulfilling its obligations under a One Time Purchase contract.

- **8. REQUIRED DOCUMENTS:** All of the items checked below must be provided to the Purchasing Division by the Vendor as specified below.

a

|                                        | <b>BID BOND:</b> All Vendors shall furnish a bid bond in the amount of five percent (5%) of the total amount of the bid protecting the State of West Virginia. The bid bond must be submitted with the bid.                                                                                                                                                                                                                                                                                                       |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | PERFORMANCE BOND: The apparent successful Vendor shall provide a performance bond in the amount of . The performance bond must be issued and received by the Purchasing Division prior to Contract award. On construction contracts, the performance bond must be 100% of the Contract value.                                                                                                                                                                                                                     |

|                                        | <b>LABOR/MATERIAL PAYMENT BOND:</b> The apparent successful Vendor shall provide a labor/material payment bond in the amount of 100% of the Contract value. The labor/material payment bond must be issued and delivered to the Purchasing Division prior to Contract award.                                                                                                                                                                                                                                      |

| certifie<br>or irre<br>same<br>labor/r | of the Bid Bond, Performance Bond, and Labor/Material Payment Bond, the Vendor may provide ed checks, cashier's checks, or irrevocable letters of credit. Any certified check, cashier's check, vocable letter of credit provided in lieu of a bond must be of the same amount and delivered on the schedule as the bond it replaces. A letter of credit submitted in lieu of a performance and material payment bond will only be allowed for projects under \$100,000. Personal or business are not acceptable. |

|                                        | <b>MAINTENANCE BOND:</b> The apparent successful Vendor shall provide a two (2) year maintenance bond covering the roofing system. The maintenance bond must be issued and delivered to the Purchasing Division prior to Contract award.                                                                                                                                                                                                                                                                          |

| $\checkmark$                           | WORKERS' COMPENSATION INSURANCE: The apparent successful Vendor shall have appropriate workers' compensation insurance and shall provide proof thereof upon request.                                                                                                                                                                                                                                                                                                                                              |

| $\checkmark$                           | <b>INSURANCE:</b> The apparent successful Vendor shall furnish proof of the following insurance prior to Contract award and shall list the state as a certificate holder:                                                                                                                                                                                                                                                                                                                                         |

|                                        | Commercial General Liability Insurance:  \$1,000,000.00  Builders Risk Insurance: builders risk – all risk insurance in an amount equal to 100% of the amount of the Contract.                                                                                                                                                                                                                                                                                                                                    |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| contained in the specifications prior to Contract award regardless of whether or not that insurance requirement is listed above.                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LICENSE(S) / CERTIFICATIONS / PERMITS: In addition to anything required under the Section entitled Licensing, of the General Terms and Conditions, the apparent successful Vendor shall furnish proof of the following licenses, certifications, and/or permits prior to Contract award, in a form acceptable to the Purchasing Division. |

|                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                           |

The apparent successful Vendor shall also furnish proof of any additional insurance requirements

The apparent successful Vendor shall also furnish proof of any additional licenses or certifications contained in the specifications prior to Contract award regardless of whether or not that requirement is listed above.

- 9. LITIGATION BOND: The Director reserves the right to require any Vendor that files a protest of an award to submit a litigation bond in the amount equal to one percent of the lowest bid submitted or \$5,000, whichever is greater. The entire amount of the bond shall be forfeited if the hearing officer determines that the protest was filed for frivolous or improper purpose, including but not limited to, the purpose of harassing, causing unnecessary delay, or needless expense for the Agency. All litigation bonds shall be made payable to the Purchasing Division. In lieu of a bond, the protester may submit a cashier's check or certified check payable to the Purchasing Division. Cashier's or certified checks will be deposited with and held by the State Treasurer's office. If it is determined that the protest has not been filed for frivolous or improper purpose, the bond or deposit shall be returned in its entirety.

- 10. ALTERNATES: Any model, brand, or specification listed herein establishes the acceptable level of quality only and is not intended to reflect a preference for, or in any way favor, a particular brand or vendor. Vendors may bid alternates to a listed model or brand provided that the alternate is at least equal to the model or brand and complies with the required specifications. The equality of any alternate being bid shall be determined by the State at its sole discretion. Any Vendor bidding an alternate model or brand should clearly identify the alternate items in its bid and should include manufacturer's specifications, industry literature, and/or any other relevant documentation demonstrating the equality of the alternate items. Failure to provide information for alternate items may be grounds for rejection of a Vendor's bid.

- 11. EXCEPTIONS AND CLARIFICATIONS: The Solicitation contains the specifications that shall form the basis of a contractual agreement. Vendor shall clearly mark any exceptions, clarifications, or

other proposed modifications in its bid. Exceptions to, clarifications of, or modifications of a requirement or term and condition of the Solicitation may result in bid disqualification.

**12. LIQUIDATED DAMAGES:** Vendor shall pay liquidated damages in the amount for

This clause shall in no way be considered exclusive and shall not limit the State or Agency's right to pursue any other available remedy.

- 13. ACCEPTANCE/REJECTION: The State may accept or reject any bid in whole, or in part. Vendor's signature on its bid signifies acceptance of the terms and conditions contained in the Solicitation and Vendor agrees to be bound by the terms of the Contract, as reflected in the Purchase Order, upon receipt.

- 14. REGISTRATION: Prior to Contract award, the apparent successful Vendor must be properly registered with the West Virginia Purchasing Division and must have paid the \$125 fee if applicable.

- 15. COMMUNICATION LIMITATIONS: In accordance with West Virginia Code of State Rules §148-1-6.6, communication with the State of West Virginia or any of its employees regarding this Solicitation during the solicitation, bid, evaluation or award periods, except through the Purchasing Division, is strictly prohibited without prior Purchasing Division approval. Purchasing Division approval for such communication is implied for all agency delegated and exempt purchases.

- 16. FUNDING: This Contract shall continue for the term stated herein, contingent upon funds being appropriated by the Legislature or otherwise being made available. In the event funds are not appropriated or otherwise made available, this Contract becomes void and of no effect beginning on July 1 of the fiscal year for which funding has not been appropriated or otherwise made available.

- 17. PAYMENT: Payment in advance is prohibited under this Contract. Payment may only be made after the delivery and acceptance of goods or services. The Vendor shall submit invoices, in arrears, to the Agency at the address on the face of the purchase order labeled "Invoice To."

- 18. UNIT PRICE: Unit prices shall prevail in cases of a discrepancy in the Vendor's bid.

- 19. **DELIVERY:** All quotations are considered freight on board destination ("F.O.B. destination") unless alternate shipping terms are clearly identified in the bid. Vendor's listing of shipping terms that contradict the shipping terms expressly required by this Solicitation may result in bid disqualification.

- **20. INTEREST:** Interest attributable to late payment will only be permitted if authorized by the West Virginia Code. Presently, there is no provision in the law for interest on late payments.

- 21. PREFERENCE: Vendor Preference may only be granted upon written request and only in accordance with the West Virginia Code § 5A-3-37 and the West Virginia Code of State Rules. A Resident Vendor Certification form has been attached hereto to allow Vendor to apply for the preference. Vendor's

- failure to submit the Resident Vendor Certification form with its bid will result in denial of Vendor Preference. Vendor Preference does not apply to construction projects.

- 22. SMALL, WOMEN-OWNED, OR MINORITY-OWNED BUSINESSES: For any solicitations publicly advertised for bid on or after July 1, 2012, in accordance with West Virginia Code §5A-3-37(a)(7) and W. Va. CSR § 148-22-9, any non-resident vendor certified as a small, women-owned, or minority-owned business under W. Va. CSR § 148-22-9 shall be provided the same preference made available to any resident vendor. Any non-resident small, women-owned, or minority-owned business must identify itself as such in writing, must submit that writing to the Purchasing Division with its bid, and must be properly certified under W. Va. CSR § 148-22-9 prior to submission of its bid to receive the preferences made available to resident vendors. Preference for a non-resident small, women-owned, or minority owned business shall be applied in accordance with W. Va. CSR § 148-22-9.

- 23. TAXES: The Vendor shall pay any applicable sales, use, personal property or any other taxes arising out of this Contract and the transactions contemplated thereby. The State of West Virginia is exempt from federal and state taxes and will not pay or reimburse such taxes.

- 24. CANCELLATION: The Purchasing Division Director reserves the right to cancel this Contract immediately upon written notice to the vendor if the materials or workmanship supplied do not conform to the specifications contained in the Contract. The Purchasing Division Director may cancel any purchase or Contract upon 30 days written notice to the Vendor in accordance with West Virginia Code of State Rules § 148-1-7.16.2.

- 25. WAIVER OF MINOR IRREGULARITIES: The Director reserves the right to waive minor irregularities in bids or specifications in accordance with West Virginia Code of State Rules § 148-1-4.6.

- **26. TIME:** Time is of the essence with regard to all matters of time and performance in this Contract.

- 27. APPLICABLE LAW: This Contract is governed by and interpreted under West Virginia law without giving effect to its choice of law principles. Any information provided in specification manuals, or any other source, verbal or written, which contradicts or violates the West Virginia Constitution, West Virginia Code or West Virginia Code of State Rules is void and of no effect.

- **28. COMPLIANCE**: Vendor shall comply with all applicable federal, state, and local laws, regulations and ordinances. By submitting a bid, Vendors acknowledge that they have reviewed, understand, and will comply with all applicable law.

- 29. PREVAILING WAGE: On any contract for the construction of a public improvement, Vendor and any subcontractors utilized by Vendor shall pay a rate or rates of wages which shall not be less than the fair minimum rate or rates of wages (prevailing wage), as established by the West Virginia Division of Labor under West Virginia Code §§ 21-5A-1 et seq. and available at <a href="http://www.sos.wv.gov/administrative-law/wagerates/Pages/default.aspx">http://www.sos.wv.gov/administrative-law/wagerates/Pages/default.aspx</a>. Vendor shall be responsible for ensuring compliance with prevailing wage requirements and determining when prevailing wage

- requirements are applicable. The required contract provisions contained in West Virginia Code of State Rules § 42-7-3 are specifically incorporated herein by reference.

- **30. ARBITRATION:** Any references made to arbitration contained in this Contract, Vendor's bid, or in any American Institute of Architects documents pertaining to this Contract are hereby deleted, void, and of no effect.

- 31. MODIFICATIONS: This writing is the parties' final expression of intent. Notwithstanding anything contained in this Contract to the contrary, no modification of this Contract shall be binding without mutual written consent of the Agency, and the Vendor, with approval of the Purchasing Division and the Attorney General's office (Attorney General approval is as to form only). No Change shall be implemented by the Vendor until such time as the Vendor receives an approved written change order from the Purchasing Division.

- 32. WAIVER: The failure of either party to insist upon a strict performance of any of the terms or provision of this Contract, or to exercise any option, right, or remedy herein contained, shall not be construed as a waiver or a relinquishment for the future of such term, provision, option, right, or remedy, but the same shall continue in full force and effect. Any waiver must be expressly stated in writing and signed by the waiving party.

- 33. SUBSEQUENT FORMS: The terms and conditions contained in this Contract shall supersede any and all subsequent terms and conditions which may appear on any form documents submitted by Vendor to the Agency or Purchasing Division such as price lists, order forms, invoices, sales agreements, or maintenance agreements, and includes internet websites or other electronic documents. Acceptance or use of Vendor's forms does not constitute acceptance of the terms and conditions contained thereon.

- 34. ASSIGNMENT: Neither this Contract nor any monies due, or to become due hereunder, may be assigned by the Vendor without the express written consent of the Agency, the Purchasing Division, the Attorney General's office (as to form only), and any other government agency or office that may be required to approve such assignments. Notwithstanding the foregoing, Purchasing Division approval may or may not be required on certain agency delegated or exempt purchases.

- **35. WARRANTY**: The Vendor expressly warrants that the goods and/or services covered by this Contract will: (a) conform to the specifications, drawings, samples, or other description furnished or specified by the Agency, (b) be merchantable and fit for the purpose intended; and (c) be free from defect in material and workmanship.

- **36. STATE EMPLOYEES:** State employees are not permitted to utilize this Contract for personal use and the Vendor is prohibited from permitting or facilitating the same.

- **37. BANKRUPTCY**: In the event the Vendor files for bankruptcy protection, the State of West Virginia may deem this Contract null and void, and terminate this Contract without notice.

### 38. [RESERVED]

- 39. CONFIDENTIALITY: The Vendor agrees that it will not disclose to anyone, directly or indirectly, any such personally identifiable information or other confidential information gained from the Agency, unless the individual who is the subject of the information consents to the disclosure in writing or the disclosure is made pursuant to the Agency's policies, procedures, and rules. Vendor further agrees to comply with the Confidentiality Policies and Information Security Accountability Requirements, set forth in <a href="http://www.state.wv.us/admin/purchase/privacy/default.html">http://www.state.wv.us/admin/purchase/privacy/default.html</a>.

- **40. DISCLOSURE:** Vendor's response to the Solicitation and the resulting Contract are considered public documents and will be disclosed to the public in accordance with the laws, rules, and policies governing the West Virginia Purchasing Division. Those laws include, but are not limited to, the Freedom of Information Act found in West Virginia Code § 29B-1-1 et seq.

If a Vendor considers any part of its bid to be exempt from public disclosure, Vendor must so indicate by specifically identifying the exempt information, identifying the exemption that applies, providing a detailed justification for the exemption, segregating the exempt information from the general bid information, and submitting the exempt information as part of its bid but in a segregated and clearly Failure to comply with the foregoing requirements will result in public disclosure identifiable format. of the Vendor's bid without further notice. A Vendor's act of marking all or nearly all of its bid as exempt is not sufficient to avoid disclosure and WILL NOT BE HONORED. Vendor's act of marking a bid or any part thereof as "confidential" or "proprietary" is not sufficient to avoid disclosure and WILL NOT BE HONORED. In addition, a legend or other statement indicating that all or substantially all of the bid is exempt from disclosure is not sufficient to avoid disclosure and WILL NOT BE HONORED. Vendor will be required to defend any claimed exemption for nondisclosure in the event of an administrative or judicial challenge to the State's nondisclosure. Vendor must indemnify the State for any costs incurred related to any exemptions claimed by Vendor. Any questions regarding the applicability of the various public records laws should be addressed to your own legal counsel prior to bid submission.

- 41. LICENSING: In accordance with West Virginia Code of State Rules §148-1-6.1.7, Vendor must be licensed and in good standing in accordance with any and all state and local laws and requirements by any state or local agency of West Virginia, including, but not limited to, the West Virginia Secretary of State's Office, the West Virginia Tax Department, West Virginia Insurance Commission, or any other state agency or political subdivision. Upon request, the Vendor must provide all necessary releases to obtain information to enable the Purchasing Division Director or the Agency to verify that the Vendor is licensed and in good standing with the above entities.

- 42. ANTITRUST: In submitting a bid to, signing a contract with, or accepting a Purchase Order from any agency of the State of West Virginia, the Vendor agrees to convey, sell, assign, or transfer to the State of West Virginia all rights, title, and interest in and to all causes of action it may now or hereafter acquire under the antitrust laws of the United States and the State of West Virginia for price fixing and/or unreasonable restraints of trade relating to the particular commodities or services purchased or acquired

by the State of West Virginia. Such assignment shall be made and become effective at the time the purchasing agency tenders the initial payment to Vendor.

43. VENDOR CERTIFICATIONS: By signing its bid or entering into this Contract, Vendor certifies (1) that its bid was made without prior understanding, agreement, or connection with any corporation, firm, limited liability company, partnership, person or entity submitting a bid for the same material, supplies, equipment or services; (2) that its bid is in all respects fair and without collusion or fraud; (3) that this Contract is accepted or entered into without any prior understanding, agreement, or connection to any other entity that could be considered a violation of law; and (4) that it has reviewed this RFQ in its entirety, understands the requirements, terms and conditions, and other information contained herein. Vendor's signature on its bid also affirms that neither it nor its representatives have any interest, nor shall acquire any interest, direct or indirect, which would compromise the performance of its services hereunder. Any such interests shall be promptly presented in detail to the Agency.

The individual signing this bid on behalf of Vendor certifies that he or she is authorized by the Vendor to execute this bid or any documents related thereto on Vendor's behalf; that he or she is authorized to bind the Vendor in a contractual relationship; and that, to the best of his or her knowledge, the Vendor has properly registered with any State agency that may require registration.

| 44. | PURCHASING CARD ACCEPTANCE: The State of West Virginia currently utilizes a Purchasing               |

|-----|------------------------------------------------------------------------------------------------------|

|     | Card program, administered under contract by a banking institution, to process payment for goods and |

|     | services. The Vendor must accept the State of West Virginia's Purchasing Card for payment of all     |

|     | orders under this Contract unless the box below is checked.                                          |

| endor is not required to accept the State of West Virginia's Purchasing Card as payment for al |

|------------------------------------------------------------------------------------------------|

| oods and services.                                                                             |

- **45. VENDOR RELATIONSHIP:** The relationship of the Vendor to the State shall be that of an independent contractor and no principal-agent relationship or employer-employee relationship is contemplated or created by this Contract. The Vendor as an independent contractor is solely liable for the acts and omissions of its employees and agents. Vendor shall be responsible for selecting, supervising, and compensating any and all individuals employed pursuant to the terms of this Solicitation and resulting contract. Neither the Vendor, nor any employees or subcontractors of the Vendor, shall be deemed to be employees of the State for any purpose whatsoever. Vendor shall be exclusively responsible for payment of employees and contractors for all wages and salaries, taxes, withholding payments, penalties, fees, fringe benefits, professional liability insurance premiums, contributions to insurance and pension, or other deferred compensation plans, including but not limited to, Workers' Compensation and Social Security obligations, licensing fees, *etc.* and the filing of all necessary documents, forms and returns pertinent to all of the foregoing. Vendor shall hold harmless the State, and shall provide the State and Agency with a defense against any and all claims including, but not limited to, the foregoing payments, withholdings, contributions, taxes, Social Security taxes, and employer income tax returns.

- **46. INDEMNIFICATION:** The Vendor agrees to indemnify, defend, and hold harmless the State and the Agency, their officers, and employees from and against: (1) Any claims or losses for services rendered

by any subcontractor, person, or firm performing or supplying services, materials, or supplies in connection with the performance of the Contract; (2) Any claims or losses resulting to any person or entity injured or damaged by the Vendor, its officers, employees, or subcontractors by the publication, translation, reproduction, delivery, performance, use, or disposition of any data used under the Contract in a manner not authorized by the Contract, or by Federal or State statutes or regulations; and (3) Any failure of the Vendor, its officers, employees, or subcontractors to observe State and Federal laws including, but not limited to, labor and wage and hour laws.

- 47. PURCHASING AFFIDAVIT: In accordance with West Virginia Code § 5A-3-10a, all Vendors are required to sign, notarize, and submit the Purchasing Affidavit stating that neither the Vendor nor a related party owe a debt to the State in excess of \$1,000. The affidavit must be submitted prior to award, but should be submitted with the Vendor's bid. A copy of the Purchasing Affidavit is included herewith.

- 48. ADDITIONAL AGENCY AND LOCAL GOVERNMENT USE: This Contract may be utilized by and extends to other agencies, spending units, and political subdivisions of the State of West Virginia; county, municipal, and other local government bodies; and school districts ("Other Government Entities"). This Contract shall be extended to the aforementioned Other Government Entities on the same prices, terms, and conditions as those offered and agreed to in this Contract. If the Vendor does not wish to extend the prices, terms, and conditions of its bid and subsequent contract to the Other Government Entities, the Vendor must clearly indicate such refusal in its bid. A refusal to extend this Contract to the Other Government Entities shall not impact or influence the award of this Contract in any manner.

- 49. CONFLICT OF INTEREST: Vendor, its officers or members or employees, shall not presently have or acquire any interest, direct or indirect, which would conflict with or compromise the performance of its obligations hereunder. Vendor shall periodically inquire of its officers, members and employees to ensure that a conflict of interest does not arise. Any conflict of interest discovered shall be promptly presented in detail to the Agency.

- 50. REPORTS: Vendor shall provide the Agency and/or the Purchasing Division with the following reports identified by a checked box below:

Such reports as the Agency and/or the Purchasing Division may request. Requested reports may include, but are not limited to, quantities purchased, agencies utilizing the contract, total contract expenditures by agency, etc.

Quarterly reports detailing the total quantity of purchases in units and dollars, along with a listing of purchases by agency. Quarterly reports should be delivered to the Purchasing Division via email at <a href="mailto:purchasing.requisitions@wv.gov">purchasing.requisitions@wv.gov</a>.

- 51. BACKGROUND CHECK: In accordance with W. Va. Code § 15-2D-3, the Director of the Division of Protective Services shall require any service provider whose employees are regularly employed on the grounds or in the buildings of the Capitol complex or who have access to sensitive or critical information

to submit to a fingerprint-based state and federal background inquiry through the state repository. The service provider is responsible for any costs associated with the fingerprint-based state and federal background inquiry.

After the contract for such services has been approved, but before any such employees are permitted to be on the grounds or in the buildings of the Capitol complex or have access to sensitive or critical information, the service provider shall submit a list of all persons who will be physically present and working at the Capitol complex to the Director of the Division of Protective Services for purposes of verifying compliance with this provision.

The State reserves the right to prohibit a service provider's employees from accessing sensitive or critical information or to be present at the Capitol complex based upon results addressed from a criminal background check.

Service providers should contact the West Virginia Division of Protective Services by phone at (304)558-9911 for more information.

- **52. PREFERENCE FOR USE OF DOMESTIC STEEL PRODUCTS:** Except when authorized by the Director of the Purchasing Division pursuant to W. Va. Code § 5A-3-56, no contractor may use or supply steel products for a State Contract Project other than those steel products made in the United States. A contractor who uses steel products in violation of this section may be subject to civil penalties pursuant to W. Va. Code § 5A-3-56. As used in this section:

- a. "State Contract Project" means any erection or construction of, or any addition to, alteration of or other improvement to any building or structure, including, but not limited to, roads or highways, or the installation of any heating or cooling or ventilating plants or other equipment, or the supply of and materials for such projects, pursuant to a contract with the State of West Virginia for which bids were solicited on or after June 6, 2001.

- **b.** "Steel Products" means products rolled, formed, shaped, drawn, extruded, forged, cast, fabricated or otherwise similarly processed, or processed by a combination of two or more or such operations, from steel made by the open heath, basic oxygen, electric furnace, Bessemer or other steel making process.

The Purchasing Division Director may, in writing, authorize the use of foreign steel products if:

- a. The cost for each contract item used does not exceed one tenth of one percent (.1%) of the total contract cost or two thousand five hundred dollars (\$2,500.00), whichever is greater. For the purposes of this section, the cost is the value of the steel product as delivered to the project; or

- **b.** The Director of the Purchasing Division determines that specified steel materials are not produced in the United States in sufficient quantity or otherwise are not reasonably available to meet contract requirements.

with W. Va. Code § 5-19-1 et seq., and W. Va. CSR § 148-10-1 et seq., for every contract or subcontract, subject to the limitations contained herein, for the construction, reconstruction, alteration, repair, improvement or maintenance of public works or for the purchase of any item of machinery or equipment to be used at sites of public works, only domestic aluminum, glass or steel products shall be supplied unless the spending officer determines, in writing, after the receipt of offers or bids, (1) that the cost of domestic aluminum, glass or steel products is unreasonable or inconsistent with the public interest of the State of West Virginia, (2) that domestic aluminum, glass or steel products are not produced in sufficient quantities to meet the contract requirements, or (3) the available domestic aluminum, glass, or steel do not meet the contract specifications. This provision only applies to public works contracts awarded in an amount more than fifty thousand dollars (\$50,000) or public works contracts that require more than ten thousand pounds of steel products.

The cost of domestic aluminum, glass, or steel products may be unreasonable if the cost is more than twenty percent (20%) of the bid or offered price for foreign made aluminum, glass, or steel products. If the domestic aluminum, glass or steel products to be supplied or produced in a "substantial labor surplus area", as defined by the United States Department of Labor, the cost of domestic aluminum, glass, or steel products may be unreasonable if the cost is more than thirty percent (30%) of the bid or offered price for foreign made aluminum, glass, or steel products.

This preference shall be applied to an item of machinery or equipment, as indicated above, when the item is a single unit of equipment or machinery manufactured primarily of aluminum, glass or steel, is part of a public works contract and has the sole purpose or of being a permanent part of a single public works project. This provision does not apply to equipment or machinery purchased by a spending unit for use by that spending unit and not as part of a single public works project.

All bids and offers including domestic aluminum, glass or steel products that exceed bid or offer prices including foreign aluminum, glass or steel products after application of the preferences provided in this provision may be reduced to a price equal to or lower than the lowest bid or offer price for foreign aluminum, glass or steel products plus the applicable preference. If the reduced bid or offer prices are made in writing and supersede the prior bid or offer prices, all bids or offers, including the reduced bid or offer prices, will be reevaluated in accordance with this rule.

### **SPECIFICATIONS**

1. **PURPOSE AND SCOPE:** The West Virginia Purchasing Division is soliciting bids on behalf of the West Virginia Educational Broadcasting Authority (EBA) to establish a contract for the one time purchase of site-to-site connectivity between three properties of the EBA and two West Virginia Network (WVNet) locations, as well as Internet access. This will be a 3-year contract.

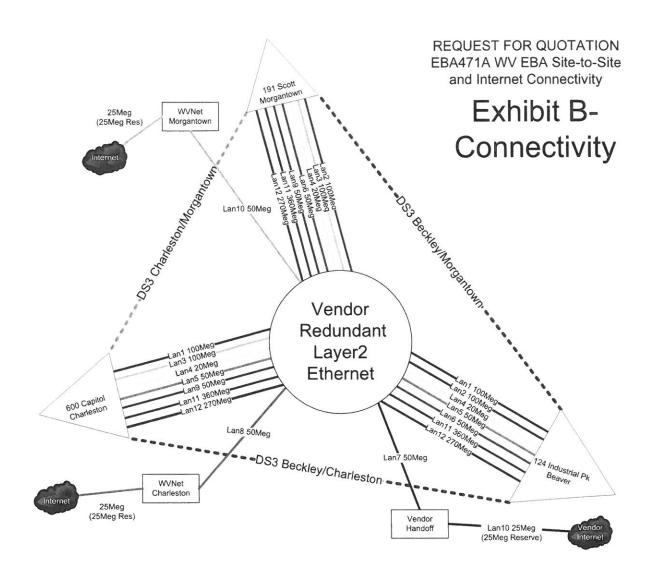

The connectivity (see exhibit B) will be used as follows:

- Layer 2 Ethernet:

- O Inter-office data and file exchange

- O Connection to the State of WV backbone

- O Teleconferencing

- O Internal video streaming

- O Content production sharing and viewing / listening

- O Equipment monitoring, including microwave systems

- O Radio broadcast and monitoring

- O Disaster recovery

- O Testing of emerging technologies to transport broadcast video over layer 2 Ethernet

- Digital Signal 3 (DS3):

- O Transport of broadcast video to transmitters

- O Transport of Production video feeds between locations

- O Transport of live broadcasts to our Master Control

- O Failover capabilities for broadcast video

- Internet Access:

- O Audio and Video streaming of current and archived content

- O Delivery of educational content to appropriate parties

- O Remote access for news reporters report from the field

- O Remote access for technical staff remote monitoring and repair from the field

- O Failover connections between locations in the event of site-to-site connectivity failures

- O General Internet Access

- 2. **DEFINITIONS:** The terms listed below shall have the meanings assigned to them below. Additional definitions can be found in section 2 of the General Terms and Conditions.

- 2.1 "Contract Item" means:

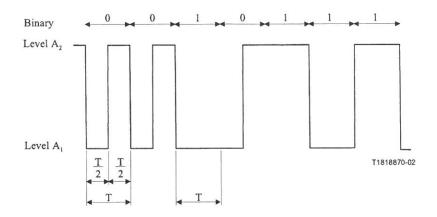

- **2.1.1 LAYER 2 ETHERNET:** Ethernet connectivity as defined by the IEEE (Institute of Electrical and Electronics Engineers) 802.3 standard and all updates to the standard regarding wired circuits.

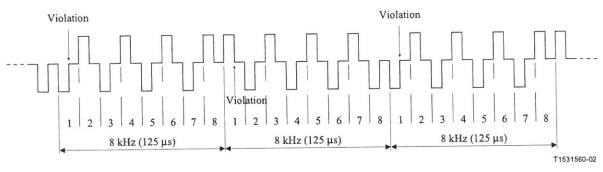

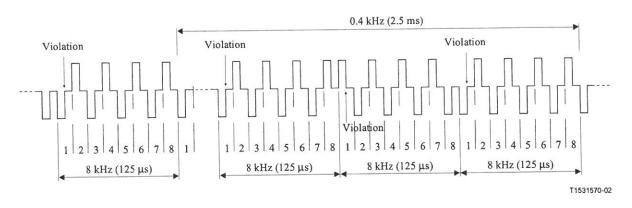

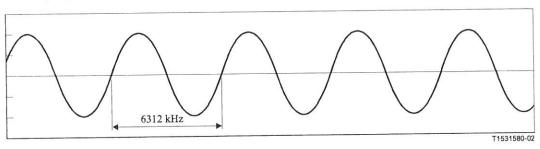

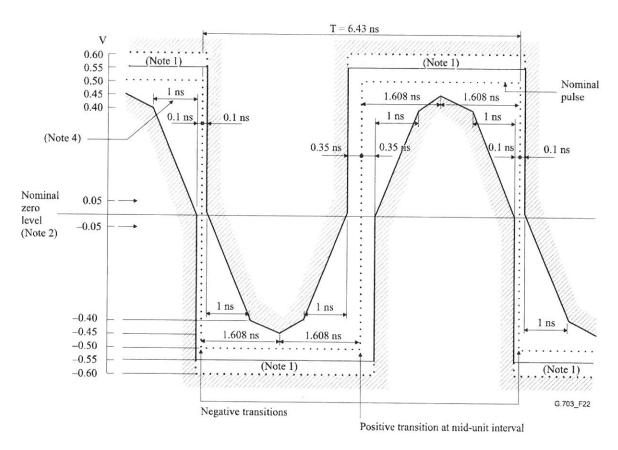

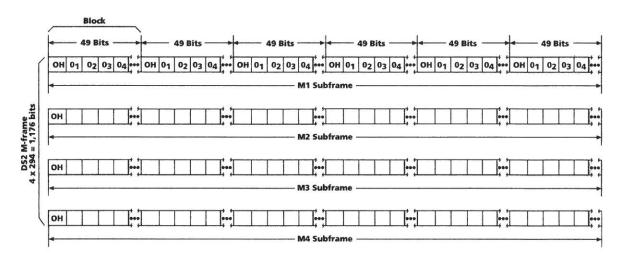

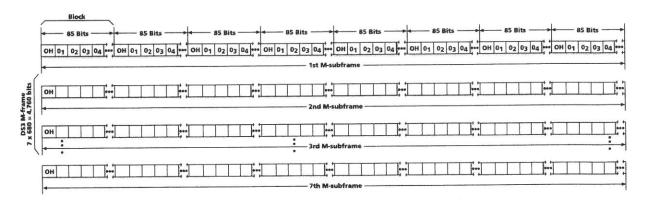

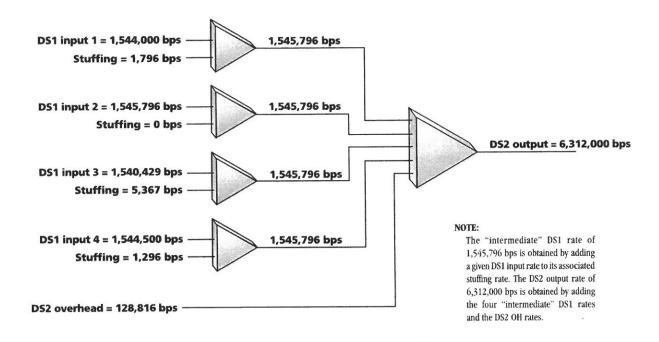

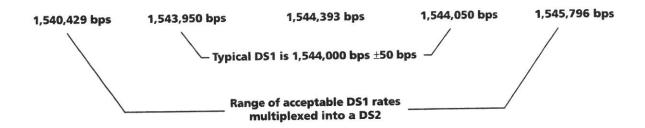

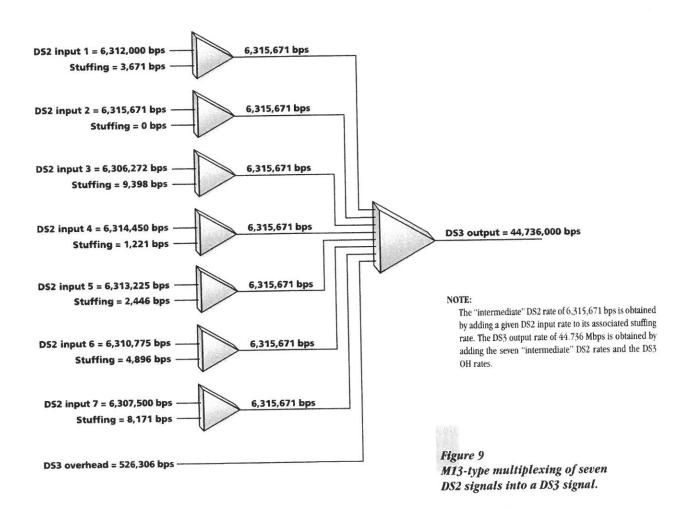

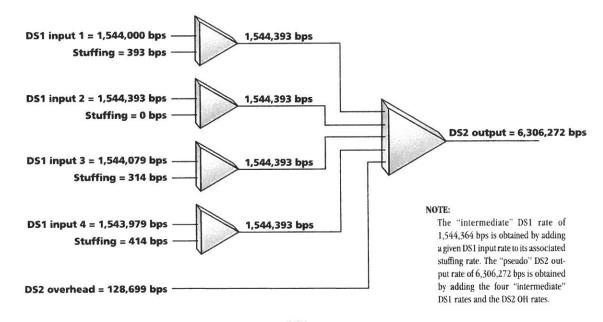

- 2.1.2 CLEAR CHANNEL DIGITAL SIGNAL 3 (DS3) CIRCUIT: Point-to-Point, full duplex, clear channel carrier meeting ITU-T (International Telecommunication Union Telecommunication Standardization Sector) G.703 specifications.

- **2.1.3 INTERNET ACCESS:** Point-of-Presence (POP) connecting Local Area Networks (LANs) to the public Internet.

- 2.2 "Pricing Page" means the pages upon which Vendor should list its proposed price for the Contract Items in the manner requested. The Pricing Page is attached hereto as Exhibit A.

- **2.3** "RFQ" means the official request for quotation published by the Purchasing Division and identified as EBA471A.

- **2.4 "QUALITY OF SERVICE (QOS)":** Quality of Service as defined by the IEEE 802.1Q standard for priority level tagging within an Ethernet frame header.

- **2.5 "REVERSE DNS (DOMAIN NAME SYSTEM)":** means reverse DNS lookup or reverse DNS resolution. It is the determination of a domain name that is associated with a given IP address using the Domain Name System of the Internet.

- **2.6 "NODE"** means a piece of equipment through which a circuit traverses creating an additional point of failure.

- **2.7 "Point of Demarcation"** means the point at which responsibility for the circuits and hardware changes from the vendor to the EBA.

### 3. GENERAL REQUIREMENTS:

3.1 Mandatory Pre-Bid Meetings: There shall be a pre-bid meeting at the Beckley offices of the EBA (124 Industrial Park Rd., Beaver WV 25813) on 05/07/2014 at 10:30 a.m. The purpose of this meeting is to discuss the contract, answer any questions vendors may have, and permit vendors to tour the facility in order to determine accurate build-out costs. There shall be a second pre-bid meeting at the Charleston offices of the EBA (600 Capitol St., Charleston, WV 25301) on 05/08/2014 at 10:30 a.m. There shall be a third pre-bid meeting at the Morgantown

offices of the EBA (191 Scott Ave., Morgantown, WV 26505) on 05/09/2014 at 11:00 a.m. The sole purpose of the second and third meetings is to tour the facilities in order to determine accurate build-out costs. Any vendor wishing to bid on this contract must attend all pre-bid meetings.

- **3.2 Subcontracting:** The vendor must own all fiber, copper wire, and equipment, and all workers must be direct employees of the vendor with the exception of approved subcontractors as defined below.

- **3.2.1** Vendor shall be wholly responsible for any subcontracted services, including but not limited to: safety, insurance, training, quality assurance, response time, and oversight.

- **3.2.2** All subcontracting must be approved by the EBA prior to proceeding. Credentials and references for any proposed subcontractors shall be provided to the WV Purchasing Division within 24 hours after bid opening.

- **3.3 All Inclusive:** Vendor must be able to provide all items and options on this RFQ to be eligible for this contract.

- **3.4 Mandatory Contract Item Requirements:** Contract Items must meet or exceed the mandatory requirements listed below.

#### 3.4.1 LAYER 2 ETHERNET

- **3.4.1.1** Circuits must meet all IEEE standards for Ethernet over wired circuits.

- 3.4.1.2 Vendor must have redundant paths for the layer 2 Ethernet circuits on its core network such that a line cut, or similar issue, will automatically failover to another path with no service interruption. The vendor shall provide a basic diagram of their core network illustrating this redundancy. This diagram must illustrate that there is no single point of failure and be acceptable to the EBA. The connection from the vendor's core network to the EBA's sites may be non-redundant.

- **3.4.1.3** Ethernet circuit shall traverse a maximum of 20 nodes from point of origin to point of termination. Vendor shall supply a list of these nodes.

- **3.4.1.4** Circuits must be compatible with all switches, routers, and other equipment using standard layer 2 Ethernet technologies.

- **3.4.1.5** Vendor must honor all EBA Quality-of-Service (QoS) assignments across the vendor's entire network. These designations must apply even when the EBA is sharing bandwidth with other vendor customers.

- 3.4.1.6 Vendor must segregate the provided 1 Gigabit Ethernet circuits into multiple RJ-45 ports of varying bandwidth and purpose. Bandwidth shall be independently guaranteed to be a minimum of stated bandwidth on all ports, with no traffic on any port affecting traffic on another port. Initial segregation will be as described in Exhibit C, Ethernet Segregation. Vendor shall, on request by the EBA, but not to exceed 1 time in a 6-month period, reconfigure this segregation at no charge. The point of demarcation shall be these ports.

### 3.4.2 DIGITAL SIGNAL 3 (DS3) CIRCUIT

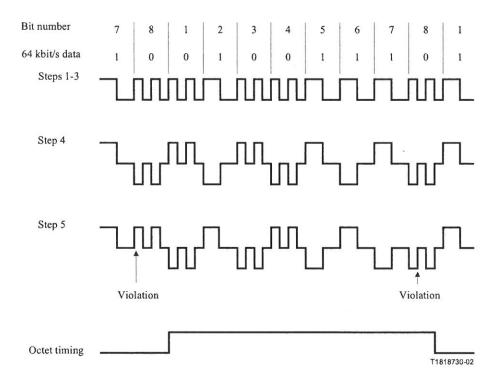

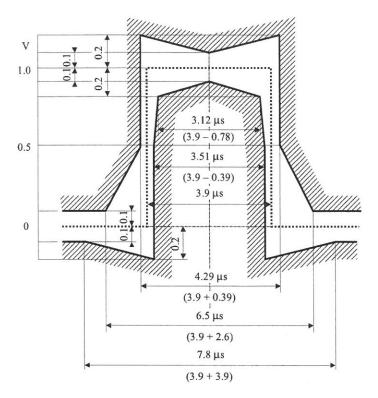

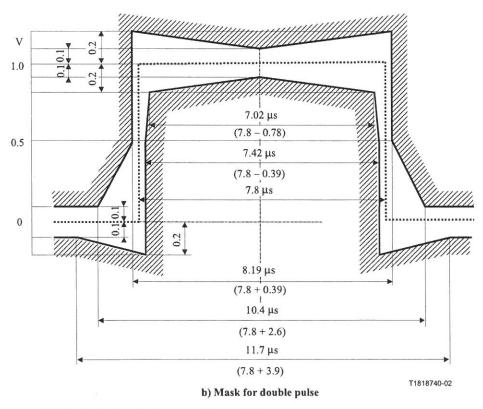

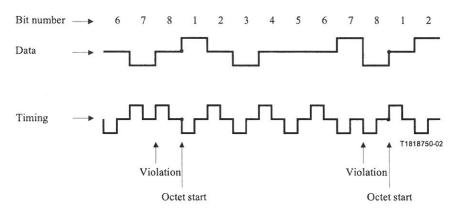

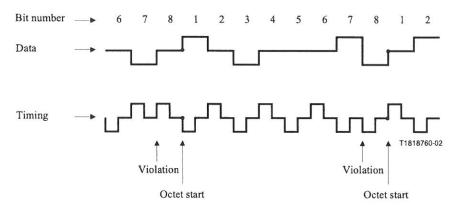

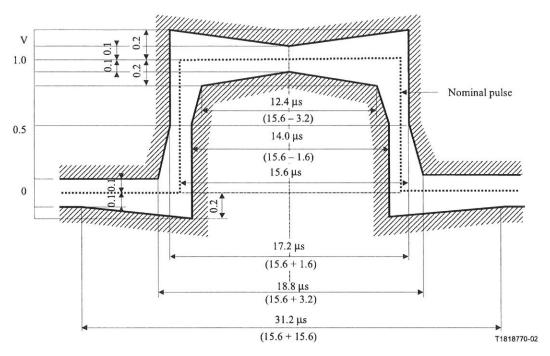

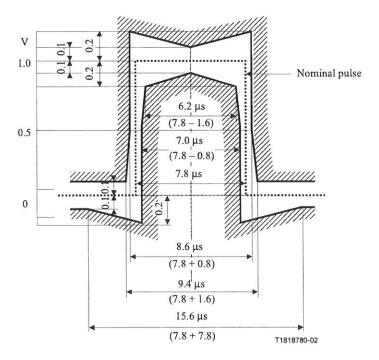

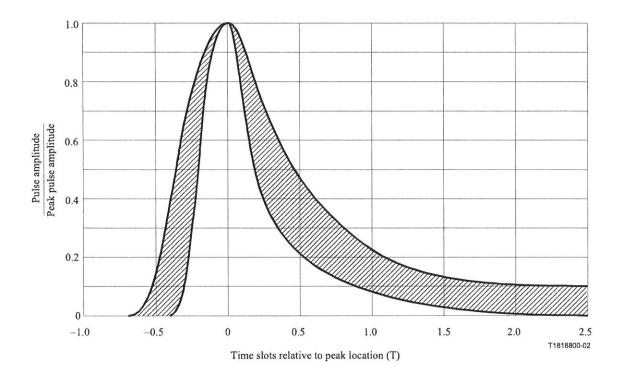

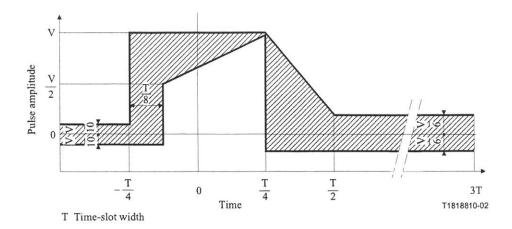

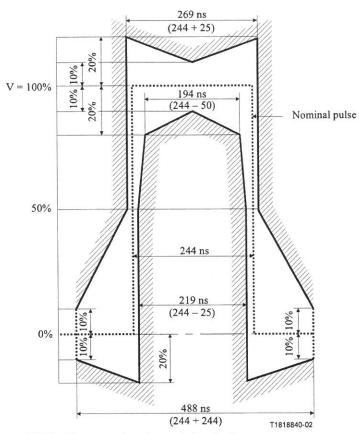

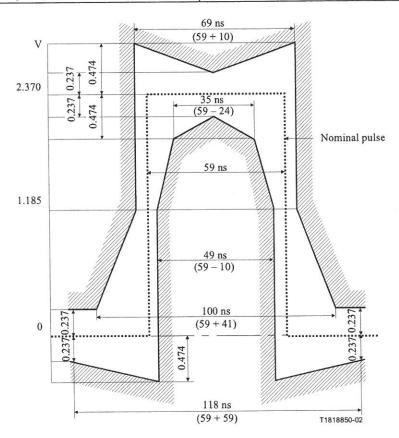

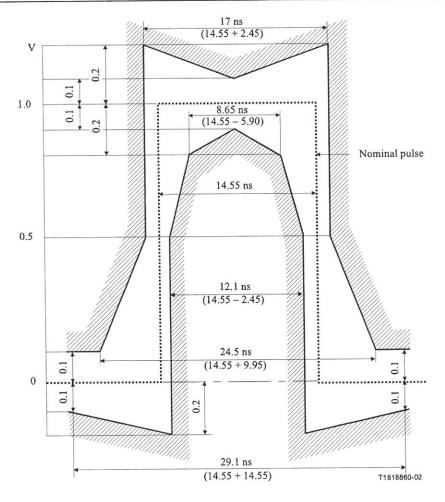

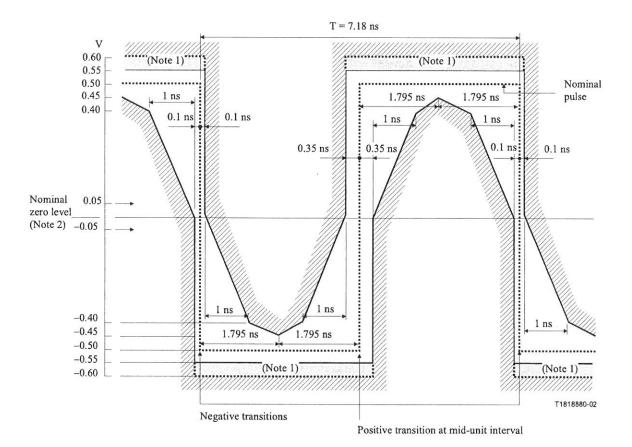

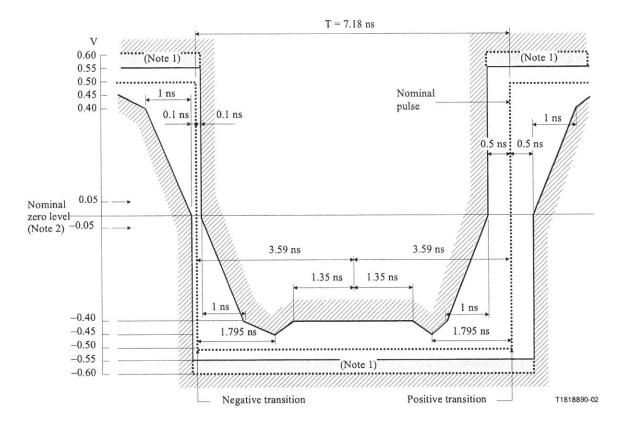

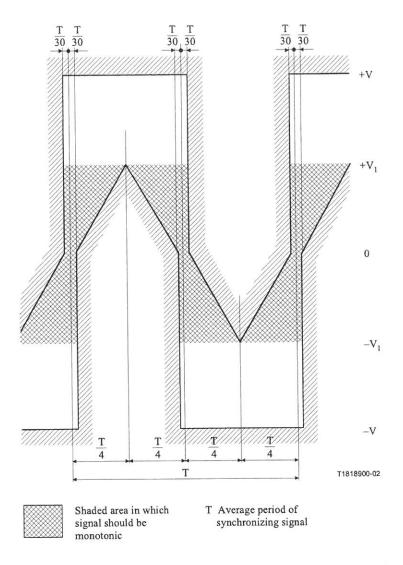

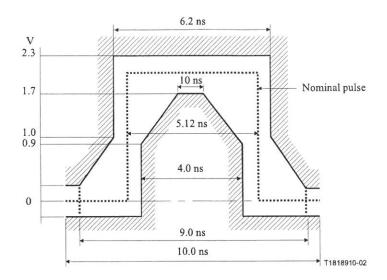

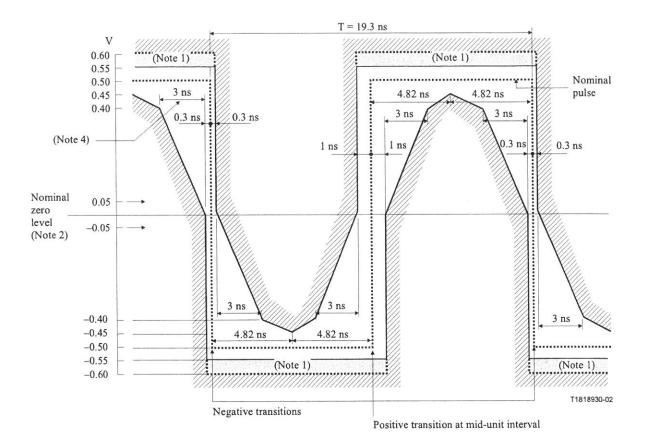

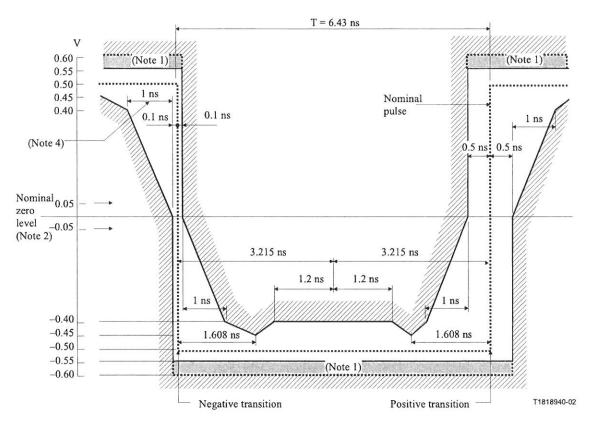

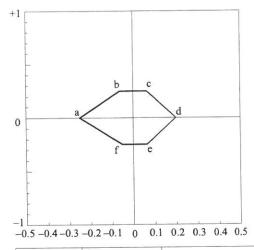

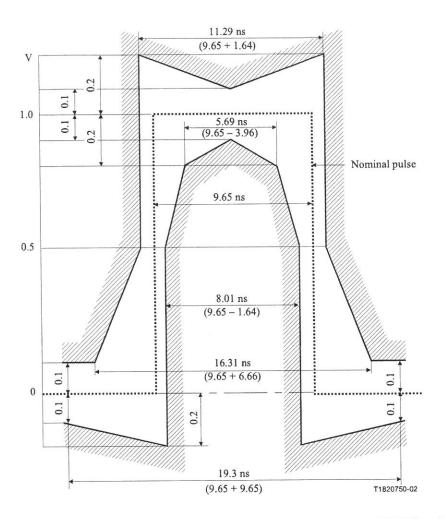

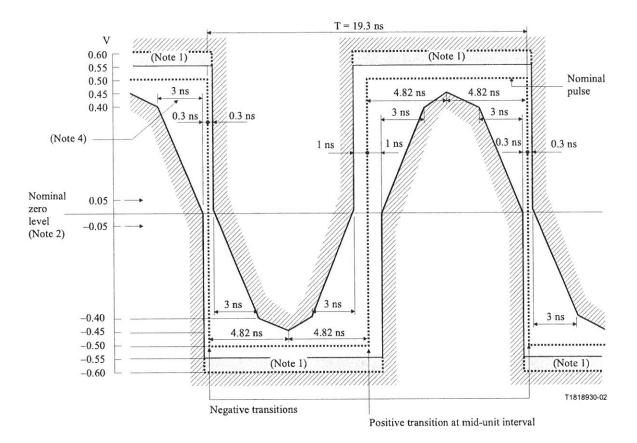

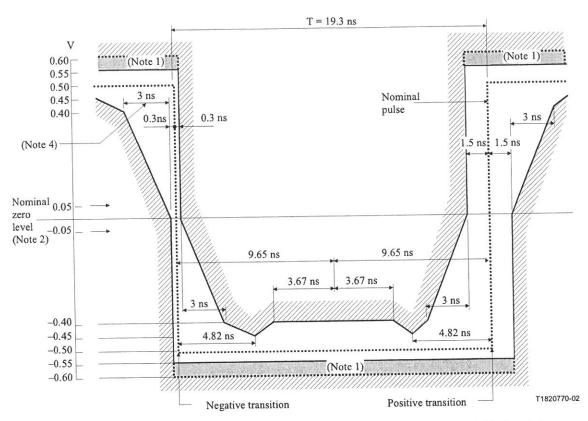

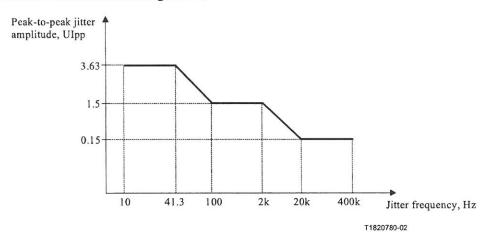

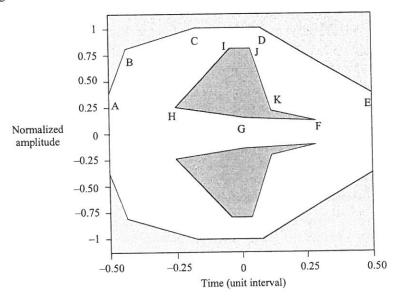

- **3.4.2.1** DS3 must meet all ITU-T specifications for G.703 circuits. See Exhibits D through G.

- **3.4.2.2** DS3 must be configured with CBIT framing as described in Exhibit H, Fundamentals of DS3, published by Telecommunications Techniques Corporation.

- **3.4.2.3** Vendor must supply timing for the DS3 circuit.

- **3.4.2.4** DS3 circuits must be full duplex; permitting separate data streams each direction.

- **3.4.2.5** DS3 circuits must terminate in 2 BNC video type connections; 1 transmit connection and 1 receive connection. These connections shall be the point of demarcation.

- 3.4.2.6 Each EBA site may be the terminating point for two DS3 circuits (see Exhibit B). At each site each DS3 shall be routed such that no single failure on the vendor's core network will bring down both DS3 circuits. The vendor shall provide a basic diagram of their core network illustrating this. This diagram must illustrate that there is no single point of failure and be acceptable to the EBA. The connection from the vendor's core network to the EBA's sites may be non-redundant.

- **3.4.2.7** DS3 circuits shall traverse a maximum of 20 nodes from point of origin to point of termination. Vendor shall supply a list of these nodes.

### 3.4.3 INTERNET CONNECTIVITY

- **3.4.3.1** Internet connections must be full duplex; stated bandwidth both directions.

- **3.4.3.2** Vendor must assign a class C subnet of 256 public IP numbers (minimum) for use by the EBA. Reverse DNS (Domain Name System) configurations for this subnet will be maintained by the EBA with the Vendor transferring this information to its own servers via zone transfers.

- **3.4.3.3** Vendor must support eBGP (external Border Gateway Protocol) for failover of public IP traffic to a 3<sup>rd</sup> party's Internet service.

- **3.4.3.3.1** Vendor must cooperate / coordinate with any parties necessary to configure and test these failover capabilities.

- **3.4.3.3.2** For failover purposes, vendor must permit the 3<sup>rd</sup> party Internet provider to announce all vendor-owned public IP's assigned to the EBA.

- **3.4.3.3.3** Upon completion of circuits and notification by the EBA, vendor will configure this failover in a timely manner.

- 3.5 Service Level Commitments: Vendor shall price their circuits such that they shall meet all the following requirements:

#### 3.5.1 Monitoring:

- 3.5.1.1 Vendor should monitor all circuits for latency, packet loss, and up time. Any available statistics shall be provided to the EBA with their monthly invoice showing the average latency, percentage packet loss, and percentage up time for the billing cycle. If available, these statistics will also be provided to the EBA for any time period upon request. If vendor is unable to monitor any of these service specifications, the vendor will accept the statistics resulting from the EBA's own monitoring.

- 3.5.1.2 If statistics provided by vendor differ from those resulting from the EBA's own monitoring, vendor shall work with the EBA to determine which statistics are accurate. These agreed-upon statistics shall be used to determine if service level commitments are met. If an agreement cannot be reached, the statistics from the EBA's monitoring shall be used to determine if service level commitments are met.

- **3.5.2** Latency: all circuits must have a maximum of 76 milliseconds of network latency (one-way delay).

- 3.5.3 Packet Loss: Packet delivery is the transit of packets between points of demarcation on the vendor's network. Packet loss is the percentage of packets not reaching their destination. This shall be calculated as ((total forwarded packets total received packets) / total forwarded packets) x 100. Packet loss must be a maximum of 0.1% when usage on a circuit is less than 100% of its stated bandwidth.

- **3.5.4 Bandwidth:** all circuits must perform at their stated bandwidth or higher at all times.

- **3.5.5** Target Circuit Availability: all circuits must have a minimum target circuit availability of 99.99%.

- 3.5.6 Mean Time to Repair: all circuits must have a maximum mean time to repair of 4 hours. Time to repair shall begin when the EBA reports the problem to the vendor and end when the vendor notifies the EBA the repair is complete. Repair completion must be verified by the EBA to be considered final.

- 3.5.7 Centralized Point of Contacts: The vendor shall provide one point of contact for all trouble, repair, and performance issues; and one point of contact for all billing and financial issues. Each point of contact shall be the appropriate party without multiple transfers to resolve issues. The vendor may provide a web portal as an additional means of monitoring, reviewing, and reporting issues.

#### 3.5.8 Service Level Credits:

3.5.8.1 If a circuit is down for more than an hour three times or more in any 30 calendar day period vendor shall credit the EBA one month's charges for that circuit.

- 3.5.8.2 If the mean time to repair is more than 4 hours for any circuit in any 12-month period, vendor shall credit the EBA 10% of the monthly cost of the circuit plus 10% for each additional hour over 5 hours. Fifteen minutes or more shall constitute an additional hour for these calculations. The credit shall not exceed the monthly cost of the circuit.

- **3.5.8.3** If a circuit doesn't meet the latency or packet loss commitments as described in sections 3.5.2 and 3.5.3, the vendor shall credit the EBA 25% of the monthly cost of the circuit until such time as these commitments are met.

- 3.5.8.4 If a circuit fails to perform at its stated bandwidth vendor shall reduce the daily costs on the circuit by the same percentage as the bandwidth deficiency. For example: if a Gigabit Ethernet circuit performs at 900 Mb instead of 1000 Mb, it is performing at a 10% deficiency, and would require a 10% daily credit. This credit shall be provided until bandwidth issues are resolved, as documented through trouble tickets.

- **3.5.8.5** The EBA must request applicable credits within 30 calendar days of receiving the invoice for the billing cycle in which the applicable event occurred.

- **3.5.8.6** Credits shall never exceed the monthly cost of the circuit in any billing cycle.

- **3.5.8.7** Credits shall never exceed 25% of the yearly cost of the circuit for any contract year.

- 3.5.8.8 Vendor will not be responsible for failures to meet Service Level Commitments under the following conditions: (a) interruptions or delays due to failure by the EBA to release services for testing and/or repair; (b) failure of power or equipment for which the

EBA is responsible; (c) delays caused by the EBA not providing timely access to the premises at which the circuits terminate; (d) interruptions or delays as a result of authorized maintenance by the EBA.

### 4. CONTRACT AWARD:

- **4.1 Contract Award:** The Contract is intended to provide the EBA with a purchase price for the Contract Items. The Contract shall be awarded to the Vendor that provides the Contract Items meeting the required specifications for the lowest overall total cost as shown on the Pricing Pages (Exhibit A).

- **4.2 Pricing Pages:** Vendor should complete the Pricing Pages (Exhibit A) by filling in the appropriate spaces in each column. Vendor should complete the Pricing Page in full as failure to complete the Pricing Pages in their entirety may result in Vendor's bid being disqualified.

Vendor should type or electronically enter the information into the Pricing Pages to prevent errors in the evaluation.

Costs must include ALL charges, including any fees, government surcharges, taxes, travel, or any other charge associated with the service. The vendor will only be paid what is on the Pricing Pages.

Price of options shall be a factor in determining the winning bidder on this RFO.

Vendor must allow the EBA to order any option at the quoted cost any time during the first 12 months of this contract. Such orders would be an addendum to the primary order, and would expire concurrently.

Notwithstanding the foregoing, the Purchasing Division may correct errors as it deems appropriate.

#### 5. DELIVERY AND RETURN:

### 5.1 Shipment and Delivery/Installation:

- 5.1.1 Vendor shall commence installation of the Contract Items immediately after being awarded this Contract and receiving a purchase order or notice to proceed. Vendor shall complete installation of the Contract Items within 45 working days after receiving a purchase order or notice to proceed. Contract Items must be delivered / installed to the EBA at the locations listed on the Pricing Pages (exhibit A). The EBA shall not be responsible for any damage, theft, or loss of equipment or other materials belonging to the vendor during the period of installation.

- 5.1.2 Verification of Installation: The EBA shall have 60 days from the time circuits are installed and functioning to test all circuits. If all circuits test successfully, monthly billing shall commence at the end of this 60-day test period. If any circuit fails to meet requirements or function as needed, the vendor will have 45 days to remedy the situation. If the vendor fails remediation, the EBA may, at its own discretion, cancel the contract with no penalty. In this situation the EBA may only be charged a maximum of the non-recurring charges (NRC's) listed on the pricing page. If the vendor remedies the situation, monthly billing will commence on the date of remedy.

- 5.2 Late Delivery/Installation: The EBA must be notified in writing if the delivery/installation of the Contract Items will be delayed for any reason. Any delay in delivery/installation that could cause harm to the EBA will be grounds for cancellation of the Contract, and/or obtaining the Contract Items from a third party.